### **Table of contents**

| 1              | 1 General information                                                                                                     | 2           |

|----------------|---------------------------------------------------------------------------------------------------------------------------|-------------|

| 2              | 2 Information about the immersion tin (iSn) process                                                                       | 2           |

| 3              | Intake requirements before processing immersion tin.  Intake requirements for pcbs                                        |             |

| <b>4</b><br>5  | 4.1 General information                                                                                                   | 6<br>6      |

|                | Table of figures                                                                                                          |             |

| Fi<br>Fi       | Fig. 1: condensate                                                                                                        | 3<br>3      |

| Fi<br>Fi<br>Fi | Fig. 9: not touching/ allowedFig. 10: pad touching solder mask/ not allowedFig. 10: pad touching solder mask/ not allowed | 4<br>5<br>5 |

#### 1 General information

Orders: Only on the email-address bestellung@hofstetter-pcb.de

Note: without an present order we will not proceed the

production!

• Shipping: We need to know your preferred **forwarder** (TNT, DHL, UPS, for-

warding Agency, Express Mail Service, etc.) as well as your required forwarding option (e.g. Express Mail Service with time options)

Terms of payment: 10 days or as agreed

Unauthorized payment discount will be requested

# 2 Information about the immersion tin (iSn) process

Chemistry product type: Stannatech® 2000H Atotech, horizontal system

• Formats: Min: 150 mm x 100 mm

Max: 610 mm x 600 mm (bigger formats on request)

Pcb - thickness:

Min: 0.10 mm (<0.80 mm only on request)</li>

Max: 4.50 mm

• iSn thickness: Min: 0.8 μm

Max:  $1.0 \mu m (0.8 \mu m - 1.0 \mu m \text{ with } c_{pk} = 1.33)$

Higher thickness only on request!

Note: APL Hofstetter processing exact iSn-thickness, as

requested!

iSn layer:

Pure tin (with small content of anti whisker additive - AWA)

whisker category like IPC4554, rating 5

• Solderability performance  $^{1}$ : 0.8  $\mu$ m ( $c_{pk} = 1.33$ ) 2x reflow + 1 x wave/ selective soldering

shelf life <6 months from process date of iSn

1.0  $\mu$ m ( $c_{pk}$  = 1.33) 2x reflow + 1 x wave/ selective soldering

shelf life <12 months from process date of iSn

• Storage conditions  $^2$ : 15  $\leq$  T  $\leq$  30 $^{\circ}$  C I  $\leq$  70% r.h.

• Loss of copper: ≤3.00 μm

-

<sup>&</sup>lt;sup>1</sup> lead free solder process

<sup>&</sup>lt;sup>2</sup> ZVEI professional association PCB and Electronics Systems | reference data / recommendation "storage conditions for unassembled pcbs" - dated February 2008

• Ionic contamination: After the iSn process <0.50 μg/cm² NaCl Equivalent

(measured at the APL Hofstetter test board)

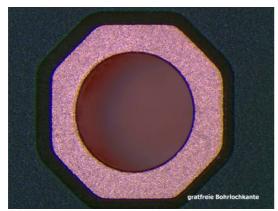

• Laser blind micro vias: Diameter min. 0.100 mm with aspect ratio max. 1:1 the drill hole

should be trapezoid, because its ideal for it.

Normal drilling holes: Diameter min 0.200 mm with aspect ratio max 1:10

### 3 Intake requirements before processing immersion tin

### 3.1 Intake requirements for pcbs

APL Hofstetter excepts only pcbs without following criteria:

- Labels

- Adhesive residues

- Pen colour (e.g. x-out identification)

- Condensate, oil, grease, fingerprints

- Paint flitters, solder mask residues

- Milling dust

- Contaminations of all kinds

- Twisting and warping

- Unclean multilayer cutback

- Mechanical defects

- Entry opportunities of liquids (such as transition in rigid-flex-areas)

Fig. 1: condensate

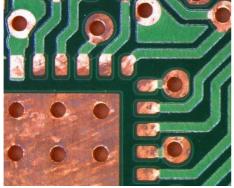

Fig. 3: finger print/ copper contamination

Fig. 2: solder mask residues

Fig. 4: mechanical defects on cooper pads

Fig. 5: crystalline liquid residues

Fig. 6: mechanical solder mask defects

### 3.2 Intake requirements for the base material

Standard FR4 and Teflon®/ PTFE materials from global, established manufacturers are easily process able. Other materials can be made only after consultation (aluminium, ceramics etc.). Following base materials can not be processed:

FR1

° FR2

° FR3

CEM1/ CEM2

#### 3.3 Intake requirements for the solder masks

#### 3.3.1 Solder mask type

All applied solder masks have to be approved for the immersion tin process by APL Hofstetter or Atotech. The solder masks have to be strictly coated according to the specifications of the lacquer manufacturer which means also that all recommendations which concern the immersion tin process have to be observed <sup>3</sup>. There will be no undercut and/ or creeping detectable after the immersion tin process if the solder mask is coated strictly under the specification of the lacquers manufacturers.

Note: In the past the solder mask type TAIYO PSR4000 G23K and similar kinds has shown massive solderability problems on the iSn coating!

#### 3.3.2 Solder mask layout

All layout work has to be done in accordance to IPC-A-600 class 3. In deviation to IPC-A-600 class 3 all holes have to be 100% open or 100% defined closed  $^4$ .

VHB\_Admin\_K\_016\_en / general\_requirements\_iSn\_en

<sup>&</sup>lt;sup>3</sup> Particularly a recommended UV - bump and/or special hardening times

<sup>&</sup>lt;sup>4</sup> ZVEI professional association PCB and Electronics Systems / reference data / recommendation "solder mask for vias" - dated March 2012

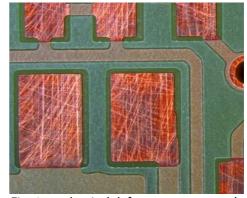

Fig. 7: 100% open hole/ allowed

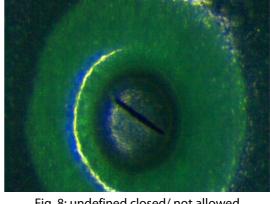

Fig. 8: undefined closed/ not allowed

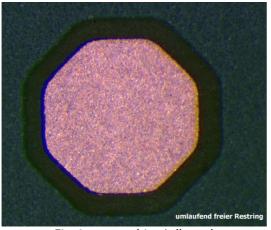

Fig. 9: not touching/allowed

Fig. 10: pad touching solder mask/ not allowed

#### 3.4 Cleanness of copper after the solder mask process

The copper surface must be free of all kind of organic and/ or inorganic residues. The surface has to be cleaned by a micro etch and/ or abrasive process. The efficiency of the copper pre-treatment has to be approved. Note: The copper removal should be  $\sim 1.0 \mu m$ .

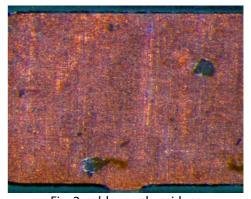

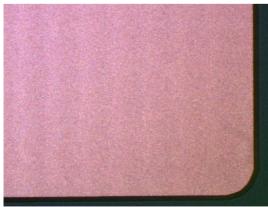

Fig. 11: clean copper surface/ allowed

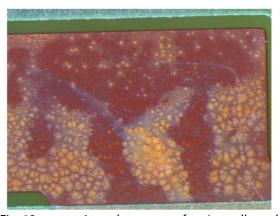

Fig. 12: contaminated copper surface/ not allowed

#### 3.5 Painting work after solder mask coating

All additional paint work should be done before the immersion tin process. The processing has to be handled strictly by the specification of the manufacturer. The varnish shall be approved for the immersion tin process.

#### 3.6 Thermal processes

All thermal processes have to be done before the immersion tin process. All thermal processes after immersion tin (heat and cold), could lead to repeated the solderability in a negative way.

#### 3.7 Ionic contamination, other contamination

The ionic contamination on pcbs at arrival at APL Hofstetter should be low as possible ( $<0.50 \mu g/cm^2$  NaCl equivalent).

### 4 Terms of delivery and packaging

#### 4.1 General information

Scribed and milled multi-panels have to be solid to minimize the risk of breaking during the immersion tin process as packaging and shipment. Paper sheets between the pcbs are not allowed because they lead to handling problems. Drying agents are neither allowed because of the risk of corrosion and/ or mechanical damages.

#### 4.2 Packaging of incoming and outgoing pcbs 5.

The packaging units have to be solid for re-using and further transportation to the customers. A bigger amount of packages has to be delivered on an euro-palette. All packaging units including the content should be packed solid to protect the good against damaging. It is necessary to pack the pcbs with damping materials (damping material should be dust and lint free). The pcbs in the packaging units have to be shrunk in suitable packages (min. 10 up to max. 25 units).

## 5 Disclaimer of warranty

APL Hofstetter assumes no warranty for all defects which results from disregarding the general requirements, subsequent manipulation of the immersion tin layer and defects from the previous circuit board manufactures.

-

<sup>&</sup>lt;sup>5</sup> All the packaging materials used, may not influence the pcbs in any way negative.